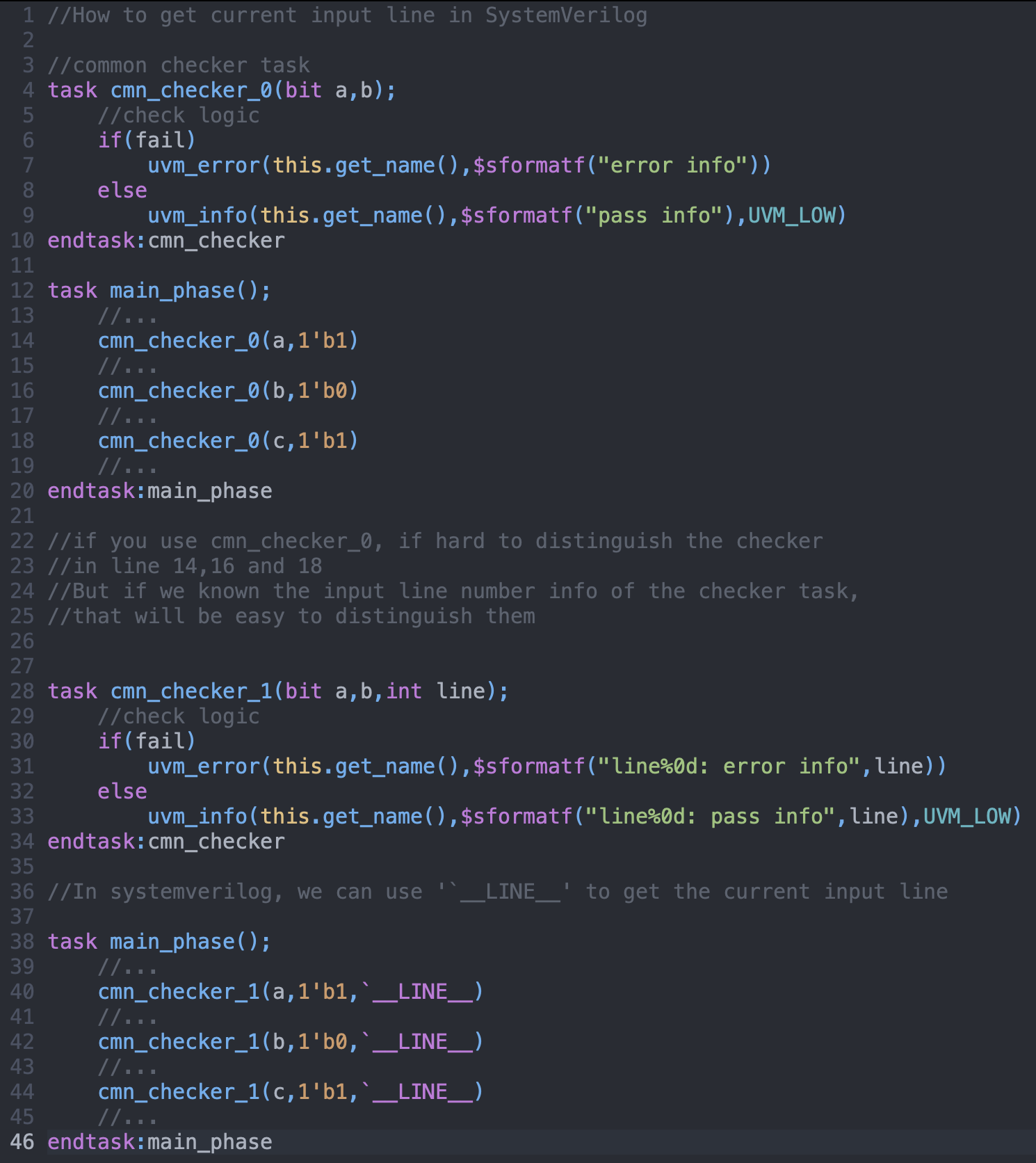

有时,在验证环境中添加打印信息时,希望知道当前打印语句在文件哪一行,或者某 task 被重复调用时,想知道某条打印信息具体由哪一次 task 调用输出的,例如,有如下 task:

...

task cmn_chk_0(bit exp);

bit act;

uvm_hdl_read(signal_scope,act);

if(act==exp)

uvm_info(this.get_name(),$sformatf("act=%0b,exp=%0b",act,exp),UVM_LOW)

else

uvm_error(this.get_name(),$sformatf("act=%0b,exp=%0b",act,exp))

endtask:cmn_chk_0

...cmn_chk_0() 在 main_phase 的不同位置被调用:

...

cmn_chk_0(1'b1);//0

...

cmn_chk_0(1'b0);//1

...

cmn_chk_0(1'b0);//2

...

cmn_chk_0(1'b1);//3

...那么当有 uvm_error 报告时,具体是哪一次调用上报的,是比较难区分的,这给 debug 带来了麻烦。

systemverilog 中可以使用 `__LINE__ 来获取当前所在的 line number,那么 check task 及其调用可写成如下形式,这样,每一次task调用所在的 line number 都可以输出在打印信息里,方便区分:

...

task cmn_chk_0(bit exp, int line);

bit act;

uvm_hdl_read(signal_scope,act);

if(act==exp)

uvm_info(this.get_name(),$sformatf("line_%0d,act=%0b,exp=%0b",line,act,exp),UVM_LOW)

else

uvm_error(this.get_name(),$sformatf("line_%0d,act=%0b,exp=%0b",line,act,exp))

endtask:cmn_chk_0

...

/////////////

//each uvm_info or uvm_error will print the input line of each 'cmn_chk_0'

...

cmn_chk_0(1'b1,`__LINE__);//0

...

cmn_chk_0(1'b0,`__LINE__);//1

...

cmn_chk_0(1'b0,`__LINE__);//2

...

cmn_chk_0(1'b1,`__LINE__);//3

...

评论 (0)